Difference between revisions of "FPGA Reader"

Senderovich (talk | contribs) m |

Senderovich (talk | contribs) m |

||

| Line 1: | Line 1: | ||

= (011) Read Packet = | = (011) Read Packet = | ||

| − | This block performs the initial reading of the packet. It skips through the packet header and reads the first two bytes of the payload, which contain the target location and packet type. (The latter is not to be confused with the packet type specified in the packet header. Our packets have a separate branding convention.) Based on these, the module will reject the packet (request a "skip" of the packet in the receive FIFO buffer) if the packet's contents will not be necessary further. The Reader will return control to the [[FPGA_Idler|Idler (010)]] if the packet is not addressed to its location or the packet type is invalid. Otherwise it will yield control to the module relevant to the packet type. | + | This block performs the initial reading of the packet. It skips through the packet header and reads the first two bytes of the payload, which contain the target location and packet type. (The latter is not to be confused with the packet type specified in the packet header. Our packets have a separate branding convention.) Based on these, the module will reject the packet (request a "skip" of the packet in the receive FIFO buffer) if the packet's contents will not be necessary further. The Reader will return control to the [[FPGA_Idler|Idler (010)]] if the packet is not addressed to its location or the [[Ethernet_packets|packet type]] is invalid. Otherwise it will yield control to the module relevant to the packet type. This selection is diagrammed in the adjacent figure. |

| − | [[Image:ReaderProcess.png| | + | [[Image:ReaderProcess.png|thumb|236px|Process flow of the Reader module. "my_Loc" represents either the constant 8-bit value hard-coded into the slot to which the digital board is attached or the wild card: 0xFF]] |

| − | + | As implied in the diagram, packet types R and Q (Reset and Query respectively) do no carry any data for the FPGA: their role is to order reset or request feedback from the sensor chips. Soft Reset and Programmer, on the other hand require certain reset/configuration data and DAC voltage values respectively, so these packets are kept. (It becomes the responsibility of these modules to dismiss these packets when finished.) | |

| − | + | Instead of implementing MAC address filtering, necessitating a lookup table of MAC address to Energy channel group, it was seen as more convenient to include an 8-bit bus into the slots for the digital boards, each hard-wired to hold a unique location value. Knowing the number of energy channels controlled on each board, the packet addressing is straightforward. Packet filtering is also made easy for the Reader: it requires a simple 8-bit comparison between the hard-coded value and that in the first byte of the packet payload. | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | + | == Programming Details == | |

| + | Note that after stepping through the 14 bytes of the packet header and reading the first two bytes of the payload it leaves the receive (Rx) buffer pointer on the 17th byte (or 3rd byte of payload). The Soft Reset and Programmer modules can continue reading with the auto-read interface to access the data relevant to them. | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | + | === Ports === | |

| − | |||

| − | |||

| − | + | * ''Clk'': [in] clock | |

| − | + | * ''/Rst'': [in] asynchronous, active-low reset | |

| − | + | ||

| − | + | ||

| − | + | [[FPGA_Registers#State_Register|State Register]] Control Lines | |

| − | + | * ''state_En'': [out] state register enable (write) signal | |

| − | + | * ''state_D'': [out] (3-bit) state register input | |

| − | + | * ''state_Q'': [in] (3-bit) state register output | |

| − | + | ||

| − | + | ||

| − | + | [[FPGA_Transceiver|Transceiver]] Control Lines | |

| − | + | * ''TxRx_Go'': [out] "Go" signal to read/write an EC control register byte | |

| − | + | * ''TxRx_RiW'': [out] active-high read, active-low write flag | |

| − | + | * ''TxRx_Aout'': [out] EC control register address (8-bit) | |

| − | + | * ''TxRx_Dout'': [out] EC control register write value | |

| − | + | * ''TxRx_Din'': [in] EC control register return value | |

| − | + | * ''TxRx_Done'': [in] "Done" signal from [[FPGA_Transceiver|Transceiver]]. | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

Revision as of 20:21, 2 June 2008

(011) Read Packet

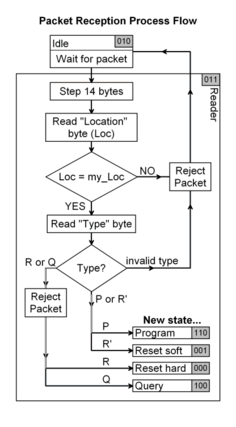

This block performs the initial reading of the packet. It skips through the packet header and reads the first two bytes of the payload, which contain the target location and packet type. (The latter is not to be confused with the packet type specified in the packet header. Our packets have a separate branding convention.) Based on these, the module will reject the packet (request a "skip" of the packet in the receive FIFO buffer) if the packet's contents will not be necessary further. The Reader will return control to the Idler (010) if the packet is not addressed to its location or the packet type is invalid. Otherwise it will yield control to the module relevant to the packet type. This selection is diagrammed in the adjacent figure.

As implied in the diagram, packet types R and Q (Reset and Query respectively) do no carry any data for the FPGA: their role is to order reset or request feedback from the sensor chips. Soft Reset and Programmer, on the other hand require certain reset/configuration data and DAC voltage values respectively, so these packets are kept. (It becomes the responsibility of these modules to dismiss these packets when finished.)

Instead of implementing MAC address filtering, necessitating a lookup table of MAC address to Energy channel group, it was seen as more convenient to include an 8-bit bus into the slots for the digital boards, each hard-wired to hold a unique location value. Knowing the number of energy channels controlled on each board, the packet addressing is straightforward. Packet filtering is also made easy for the Reader: it requires a simple 8-bit comparison between the hard-coded value and that in the first byte of the packet payload.

Programming Details

Note that after stepping through the 14 bytes of the packet header and reading the first two bytes of the payload it leaves the receive (Rx) buffer pointer on the 17th byte (or 3rd byte of payload). The Soft Reset and Programmer modules can continue reading with the auto-read interface to access the data relevant to them.

Ports

- Clk: [in] clock

- /Rst: [in] asynchronous, active-low reset

State Register Control Lines

- state_En: [out] state register enable (write) signal

- state_D: [out] (3-bit) state register input

- state_Q: [in] (3-bit) state register output

Transceiver Control Lines

- TxRx_Go: [out] "Go" signal to read/write an EC control register byte

- TxRx_RiW: [out] active-high read, active-low write flag

- TxRx_Aout: [out] EC control register address (8-bit)

- TxRx_Dout: [out] EC control register write value

- TxRx_Din: [in] EC control register return value

- TxRx_Done: [in] "Done" signal from Transceiver.