Difference between revisions of "FPGA Reader"

Senderovich (talk | contribs) m |

Senderovich (talk | contribs) m |

||

| Line 1: | Line 1: | ||

| − | + | = (011) Read Packet = | |

| + | |||

| + | This block performs the initial reading of the packet. It skips through the packet header and reads the first two bytes of the payload, which contain the target location and packet type. (The latter is not to be confused with the packet type specified in the packet header. Our packets have a separate branding convention.) Based on these, the module will reject the packet (request a "skip" of the packet in the receive FIFO buffer) if the packet's contents will not be necessary further. The Reader will return control to the [[FPGA_Idler|Idler (010)]] if the packet is not addressed to its location or the packet type is invalid. Otherwise it will yield control to the module relevant to the packet type. | ||

| + | |||

| + | [[Image:ReaderProcess.png|frame]] | ||

Block 011 is the only block with switching between following states. Its first task is to load the MAC data of the packet. If filtering inside of the FPGA is required, this block is responsible for it. The only MAC filtering likely to be needed is a check to see if the destination MAC address matches the MAC address of the CP2200/1, but the CP2200/1 should filter this itself (verify in the data sheet). If the packet is bad, this block tells the CP2200/1 to skip the packet and returns to block 010. The MAC filter would be the first substate. | Block 011 is the only block with switching between following states. Its first task is to load the MAC data of the packet. If filtering inside of the FPGA is required, this block is responsible for it. The only MAC filtering likely to be needed is a check to see if the destination MAC address matches the MAC address of the CP2200/1, but the CP2200/1 should filter this itself (verify in the data sheet). If the packet is bad, this block tells the CP2200/1 to skip the packet and returns to block 010. The MAC filter would be the first substate. | ||

| Line 18: | Line 22: | ||

|} | |} | ||

Anything other than the three defined packets is considered a bad packet and is discarded in the CP2200/1 before transitioning back to state 010. An "R" packet obtains the reset mask from the second byte then discards the packet before transitioning to state 000. State 000 assumes that the reset mask is held, so this output needs to be latched in place until the next time this block activates. A query has no switches or masks on it, so a "Q" packet will be discarded from the CP2200/1 before continuing on. A "P" packet has a large amount of data attached to it, so that is the only packet not discarded before continuing to the next state. This allows later states to access the packet data, but also puts on those later states the responsibility for discarding the packet once finished with it. | Anything other than the three defined packets is considered a bad packet and is discarded in the CP2200/1 before transitioning back to state 010. An "R" packet obtains the reset mask from the second byte then discards the packet before transitioning to state 000. State 000 assumes that the reset mask is held, so this output needs to be latched in place until the next time this block activates. A query has no switches or masks on it, so a "Q" packet will be discarded from the CP2200/1 before continuing on. A "P" packet has a large amount of data attached to it, so that is the only packet not discarded before continuing to the next state. This allows later states to access the packet data, but also puts on those later states the responsibility for discarding the packet once finished with it. | ||

| + | |||

| + | |||

| + | Stepping through the 14 bytes of the packet header and reading the first two bytes of the payload it leaves the receive (Rx) buffer pointer on the 17th byte (or 3rd byte of payload). | ||

| + | |||

inputs | inputs | ||

Revision as of 19:33, 2 June 2008

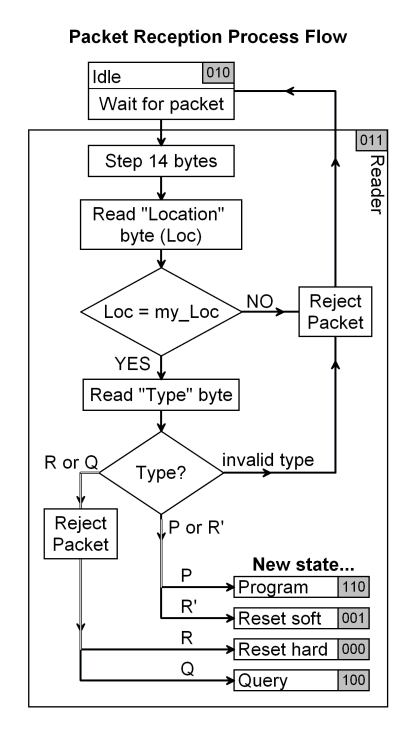

(011) Read Packet

This block performs the initial reading of the packet. It skips through the packet header and reads the first two bytes of the payload, which contain the target location and packet type. (The latter is not to be confused with the packet type specified in the packet header. Our packets have a separate branding convention.) Based on these, the module will reject the packet (request a "skip" of the packet in the receive FIFO buffer) if the packet's contents will not be necessary further. The Reader will return control to the Idler (010) if the packet is not addressed to its location or the packet type is invalid. Otherwise it will yield control to the module relevant to the packet type.

Block 011 is the only block with switching between following states. Its first task is to load the MAC data of the packet. If filtering inside of the FPGA is required, this block is responsible for it. The only MAC filtering likely to be needed is a check to see if the destination MAC address matches the MAC address of the CP2200/1, but the CP2200/1 should filter this itself (verify in the data sheet). If the packet is bad, this block tells the CP2200/1 to skip the packet and returns to block 010. The MAC filter would be the first substate.

After MAC filtering comes the second substate (or the only substate if MAC filtering is found to be unnecessary). This reads the first byte of the packet's data and uses it as a switch to determine the transition to the next state:

| ASCII | Next State | |

|---|---|---|

| R | 000 | |

| Q | 100 | |

| P | 110 | |

| other | 010 |

Anything other than the three defined packets is considered a bad packet and is discarded in the CP2200/1 before transitioning back to state 010. An "R" packet obtains the reset mask from the second byte then discards the packet before transitioning to state 000. State 000 assumes that the reset mask is held, so this output needs to be latched in place until the next time this block activates. A query has no switches or masks on it, so a "Q" packet will be discarded from the CP2200/1 before continuing on. A "P" packet has a large amount of data attached to it, so that is the only packet not discarded before continuing to the next state. This allows later states to access the packet data, but also puts on those later states the responsibility for discarding the packet once finished with it.

Stepping through the 14 bytes of the packet header and reading the first two bytes of the payload it leaves the receive (Rx) buffer pointer on the 17th byte (or 3rd byte of payload).

inputs

- Clk: clock

- /Rst: asynchronous, active-low reset

- State: 3-bit state value

- - transceiver control lines -

internal signals

- S_En: state enable, S_En <= not (St(2) or St(1) or St(0))

- Go: when S_En goes high Go pulses for one cycle

blocks

- MAC Filter

- This block checks that the MAC address in the packet destination field is the same as the MAC address of the board. If not the packet is discarded, if so then the MAC data (destination and source MAC address, packet length) are discarded and processing continues.

- inputs

- Clk: clock

- /Rst: asynchronous, active-low reset

- Go: pulse to begin

- - transceiver control lines -

- outputs

- Discard: pulse to State Advance to discard packet and return to 010

- Continue: pulse to Switch to continue processing

- - transceiver control lines -

- Switch

- This block reads the first data byte of the packet and uses it as a switch to direct the state machine to the appropriate next step.

- inputs

- Clk: clock

- /Rst: asynchronous, active-low reset

- Go: pulse to begin

- - transceiver control lines -

- outputs

- Discard: pulse to State Advance to discard packet and return to 010

- Reset_000: pulse to State Advance to discard packet and go to 000

- Query: pulse to State Advance to discard packet and go to 100

- Program: pulse to State Advance to keep packet and go to 110

- - transceiver control lines -

- State Advance

- This block has several Go lines and based on which is pulsed the next state is set up by loading a new state value into the state register. It also discards packets other than "P".

- inputs

- Clk: clock

- /Rst: asynchronous, active-low reset

- Discard: pulse to discard packet and return to 010

- Reset_000: pulse to discard packet and go to 000

- Query: pulse to discard packet and go to 100

- Program: pulse to keep packet and go to 110

- - transceiver control lines -

- outputs

- Done: pulse to signal completion; connects to state register enable

- New_St: new state to load to state register; goes to 000, 010, 100, or 110 when Done is high depending on switching

- - transceiver control lines -