Difference between revisions of "SiPM Amplifier Optimization"

Senderovich (talk | contribs) |

Senderovich (talk | contribs) (→Gain) |

||

| (14 intermediate revisions by 2 users not shown) | |||

| Line 18: | Line 18: | ||

The amplifier provided by Photonique with a gain of roughly 3 kΩ was well suited for single photon counting. However, for typical signals ranging in the hundreds of SiPM pixels, this gain excessive. However, the option of switching back to single photon detection for the purposes of calibration would be a nice feature. | The amplifier provided by Photonique with a gain of roughly 3 kΩ was well suited for single photon counting. However, for typical signals ranging in the hundreds of SiPM pixels, this gain excessive. However, the option of switching back to single photon detection for the purposes of calibration would be a nice feature. | ||

| − | From the perspective of expected signal amplitudes (taking into account optical and SiPM's quantum efficiencies) signals around 300 pixels (px) are expected. With a SiPM gain of about 2 × 10<sup>5</sup> ~ 9.6 pC are expected to be deposited. Design uncertainties that go into the full calculation summarized here can easily allow variation in this result by a factor of two or more. Roughly estimating this charge to be contained in a triangular pulse with 5 ns FWHM (after all the broadening inherent in the amplifier) yields a total signal peak of 0.5 mA. With this figure and the full range of the ADC (2V) it seems that 3 kΩ is still appropriate. However this does not leave room for variation discussed above. Instead, a goal of sub-1 kΩ gain was adopted. | + | From the perspective of expected signal amplitudes (taking into account optical and SiPM's quantum efficiencies) signals around 300 pixels (px) are expected. With a SiPM gain of about 2 × 10<sup>5</sup> ~ 9.6 pC are expected to be deposited. Design uncertainties that go into the full calculation summarized here can easily allow variation in this result by a factor of two or more. Roughly estimating this charge to be contained in a triangular pulse with <strike>5 ns</strike> 20 ns? FWHM (after all the broadening inherent in the amplifier) yields a total signal peak of 0.5 mA. With this figure and the full range of the ADC (2V) it seems that 3 kΩ is still appropriate. However this does not leave room for variation discussed above. Instead, a goal of sub-1 kΩ gain was adopted. |

For the high gain setting, the issue is mainly the vertical resolution of the ADC. For most of the duration of this project, the 8-bit version of the ADC was planned to be allocated for microscope readout, imposing a stringent requirement on gain in order to avoid the digitization noise inherent in signals only a few adc voltage steps. The 12-bit ADC makes clean readout of single pixel wavefunctions more realistic: at the most sensitive scale of 0.5 V, the resolution is 0.12 mV. However, we must also take into account noise and a possible factor of two loss in the split of the signal between the ADC and the CFD (constant fraction discriminator to prepare for time pick-off.) This time, it is appropriate to take a pessimistic scenario of the pulse shape: taking a triangular pulse with 30 ns FWHM, leading to a single pixel current peak of 0.27 μA. Under these conditions, gain of 7 kΩ is enough, giving 15 adc steps per pixel. | For the high gain setting, the issue is mainly the vertical resolution of the ADC. For most of the duration of this project, the 8-bit version of the ADC was planned to be allocated for microscope readout, imposing a stringent requirement on gain in order to avoid the digitization noise inherent in signals only a few adc voltage steps. The 12-bit ADC makes clean readout of single pixel wavefunctions more realistic: at the most sensitive scale of 0.5 V, the resolution is 0.12 mV. However, we must also take into account noise and a possible factor of two loss in the split of the signal between the ADC and the CFD (constant fraction discriminator to prepare for time pick-off.) This time, it is appropriate to take a pessimistic scenario of the pulse shape: taking a triangular pulse with 30 ns FWHM, leading to a single pixel current peak of 0.27 μA. Under these conditions, gain of 7 kΩ is enough, giving 15 adc steps per pixel. | ||

| − | |||

=== Minimal Dependence on <math>\beta</math> === | === Minimal Dependence on <math>\beta</math> === | ||

| Line 40: | Line 39: | ||

=== Short Pulses === | === Short Pulses === | ||

| − | The duration of the amplified signals is, in essence, the dead time of the channel. (Pulses with significant overlap are difficult to distinguish.) The lower bound of the pulse width is set by the scintillator. The BCF-20 intended for use in the microscope has a decay time of 2.7 ns. A somewhat stricter restriction is set by the sampling rate of the ADC - 250 MHz. A rough (and vague) guideline of 15 total signal duration has been observed during the design. | + | The duration of the amplified signals is, in essence, the dead time of the channel. (Pulses with significant overlap are difficult to distinguish.) The lower bound of the pulse width is set by the scintillator. The BCF-20 intended for use in the microscope has a decay time of 2.7 ns. A somewhat stricter restriction is set by the sampling rate of the ADC - 250 MHz. A rough (and vague) guideline of 15 ns total signal duration has been observed during the design. |

| − | |||

=== Power Consumption === | === Power Consumption === | ||

| Line 78: | Line 76: | ||

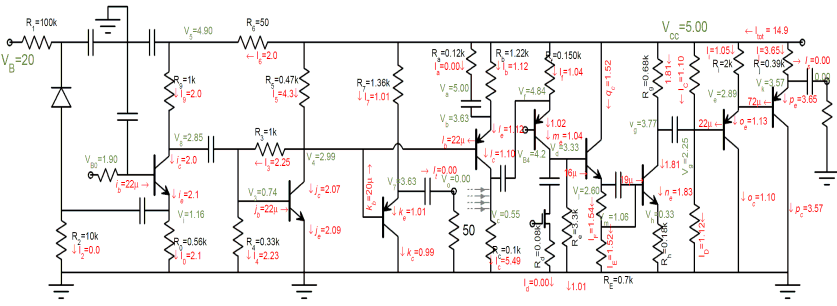

| − | [[Image: | + | [[Image:AmpCircuit_v7_DC.png|frame|center|DC characteristics of the amplifier. Units of V, mA, and Ω are implied unless corrected by different prefix.]] |

| Line 85: | Line 83: | ||

It essential to avoid clipping the signal at designed gain levels and to be able to utilize the full range (2 V) of the ADC. Appropriate DC level were set to avoid saturation any transistor collectors. This turns out a bit involved, since the collector-base voltage (plus the canonical saturation margin of 100 mV) gap necessary is more than the maximum desired signal of 2 V due to attenuation along the amplifier chain. Changing DC levels changes biasing of transistor bases, changing the quiescent current and therefore the attenuation. Additionally the power budget significantly restricts the DC levels of the circuit. | It essential to avoid clipping the signal at designed gain levels and to be able to utilize the full range (2 V) of the ADC. Appropriate DC level were set to avoid saturation any transistor collectors. This turns out a bit involved, since the collector-base voltage (plus the canonical saturation margin of 100 mV) gap necessary is more than the maximum desired signal of 2 V due to attenuation along the amplifier chain. Changing DC levels changes biasing of transistor bases, changing the quiescent current and therefore the attenuation. Additionally the power budget significantly restricts the DC levels of the circuit. | ||

| − | In the current stage of the design, full 2V range has not been achieved. Both single channel and summing outputs | + | In the current stage of the design, full 2V range has not been achieved. Both single channel and summing outputs go up to about 1.5 V. |

| − | |||

==== The Gain Switch ==== | ==== The Gain Switch ==== | ||

| − | A MOSFET | + | A MOSFET switches the effective collector resistance in the first stage of the summing circuit between about 3.3 kΩ due to R<sub>e</sub> alone and about 80 Ω for the parallel path. NXP's BF1108R has been selected for prototyping. Its typical <math>V_{GS}</math> for current pinch-off is -3 V (max: -4 V). Putting its source on the supply rail and switching the gate between 5 V (on) and 0 V (off). A bypass capacitor (not shown in diagram) near the gate lead is important to prevent spurious switching. |

| − | |||

==== Final Performance Parameters ==== | ==== Final Performance Parameters ==== | ||

With the final parameters specified by the circuit model resistor input vector set to | With the final parameters specified by the circuit model resistor input vector set to | ||

| − | <pre>R = [.56 1 .33 .47 1.36 1 .12 1.22 .1 .082 3.3 .68 | + | <pre>R = [.56 1 .33 .47 1.36 1 .12 1.22 .1 .082 3.3 .15 .68 .18 2 .392 .7 1]*1e3</pre> |

(see [[SiPM Amplifier Components]] for a complete list of component values) the following theoretical specifications are achieved: | (see [[SiPM Amplifier Components]] for a complete list of component values) the following theoretical specifications are achieved: | ||

| − | {| style="text-align:center" cellpadding=" | + | {| align="center" style="text-align:center" cellpadding="4" |

| − | ! !! Amplifier Stage !! Summing Stage !! Units !! | + | ! !! Amplifier Stage !! Summing Stage !! Units !! Notes |

|- | |- | ||

! align="left" | Gain (low/high) | ! align="left" | Gain (low/high) | ||

| − | | 0.29 || 0.29/7.5 || kΩ | + | | 0.29 || 0.29/7.5 || kΩ || 50 Ω load assumed |

|- | |- | ||

! align="left" | Input impedance | ! align="left" | Input impedance | ||

| 13.5 || 27.3 || Ω | | 13.5 || 27.3 || Ω | ||

|- | |- | ||

| − | ! align="left" | Power | + | ! align="left" | Power (quiescent) |

| 42 || 47 || mW || i.e. 52 mW/channel | | 42 || 47 || mW || i.e. 52 mW/channel | ||

|- | |- | ||

| − | ! align="left" | | + | ! align="left" | Output pulse height (max) |

| 1.46 || 1.45 || V | | 1.46 || 1.45 || V | ||

|} | |} | ||

Latest revision as of 21:42, 16 October 2011

The SiPM amplifier currently in use for SiPM characterization (Photonique item AMP_0604) must be adapted for tagger microscope use. The following is a brief outline of the design requirements. They are discussed in detail in the following sections

- adjustable gain, ranging from readout of hundreds of pixels to calibration with single-photon counting

- less than 15% gain variability on transistor () parameter

- summing circuit to pool SiPM signals in groups of 5 (readout of individual channels must not affect readout of the sum regardless of termination used)

- minimized pulse duration for higher running rates

- minimized power consumption

Design Requirements

One of the most important considerations in the amplifier design is the target data acquisition system. Currently, the microscope is slated to be read out by a 12-bit flash ADC with a 250 MHz sampling rate and range settings of -2V, -1V and -0.5V.

Gain

The amplifier provided by Photonique with a gain of roughly 3 kΩ was well suited for single photon counting. However, for typical signals ranging in the hundreds of SiPM pixels, this gain excessive. However, the option of switching back to single photon detection for the purposes of calibration would be a nice feature.

From the perspective of expected signal amplitudes (taking into account optical and SiPM's quantum efficiencies) signals around 300 pixels (px) are expected. With a SiPM gain of about 2 × 105 ~ 9.6 pC are expected to be deposited. Design uncertainties that go into the full calculation summarized here can easily allow variation in this result by a factor of two or more. Roughly estimating this charge to be contained in a triangular pulse with 5 ns 20 ns? FWHM (after all the broadening inherent in the amplifier) yields a total signal peak of 0.5 mA. With this figure and the full range of the ADC (2V) it seems that 3 kΩ is still appropriate. However this does not leave room for variation discussed above. Instead, a goal of sub-1 kΩ gain was adopted.

For the high gain setting, the issue is mainly the vertical resolution of the ADC. For most of the duration of this project, the 8-bit version of the ADC was planned to be allocated for microscope readout, imposing a stringent requirement on gain in order to avoid the digitization noise inherent in signals only a few adc voltage steps. The 12-bit ADC makes clean readout of single pixel wavefunctions more realistic: at the most sensitive scale of 0.5 V, the resolution is 0.12 mV. However, we must also take into account noise and a possible factor of two loss in the split of the signal between the ADC and the CFD (constant fraction discriminator to prepare for time pick-off.) This time, it is appropriate to take a pessimistic scenario of the pulse shape: taking a triangular pulse with 30 ns FWHM, leading to a single pixel current peak of 0.27 μA. Under these conditions, gain of 7 kΩ is enough, giving 15 adc steps per pixel.

Minimal Dependence on

Dependence of a design on a value β of a transistor is never a good idea, given its variability as a function of temperature. The value also varies between one transistor and the next. The high speed transistors necessary in this design are already at a disadvantage with respect to this design goal, due to their low beta with the result of greater significance of the parameter's variation. This issue will be discussed at length below.

While it is true that this variation can be compensated by adjusting the bias voltage on the SiPM to alter the gain, this sort of tweaking is not desirable. The detection efficiency changes right along with the gain. (Detection of the maximimum number of photons is critical for good time resolution.) With these concerns in mind, a design requirement of gain variation no greater than 15% variation was set. The bounds of overall-amplifier β variation were taken conservatively: the worst scenario was one in which all transistors are at the minimum β value.

Summing Circuit

While the microscope contains 500 optical channels resulting from the two-dimensional segmentation of the focal plane, only the energy bin information is important. The vertical column of 5 scintillating fibers in the focal plane can then have its signals summed, reducing the count of channels requiring readout to 100. However, the design of the microscope calls for individual readout in 5 columns spread around the focal plane in order to retain the knowledge of the two-dimensional orientation of the electron stripe.

Thus a summing circuit is necessary to tie together 5 amplifiers. Drivers for single channel readout must still be available on the board and their output must be available on the board's interface pins. (The choice of which group of channels can be accessed is up to the layout of the backplane board.) The individual channel and summing circuit outputs must remain independent regardless of termination. This means that the input to the summing circuit must have its own current source so that the load on the individual channel is not relevant. Additionally, as has been discussed above under gain requirements, the summing circuit must offer additional gain when system is set to high gain mode.

Short Pulses

The duration of the amplified signals is, in essence, the dead time of the channel. (Pulses with significant overlap are difficult to distinguish.) The lower bound of the pulse width is set by the scintillator. The BCF-20 intended for use in the microscope has a decay time of 2.7 ns. A somewhat stricter restriction is set by the sampling rate of the ADC - 250 MHz. A rough (and vague) guideline of 15 ns total signal duration has been observed during the design.

Power Consumption

Operation of over 500 such amplifiers (spares are available on each board) in a sealed box presents an issue of heat management. High temperatures inside the microscope should be avoided especially due to the sensitivity of SiPM parameters on temperature. Note also that the amplifiers will be packed very tightly (~5 mm strips) in the final layout. 30 mW has been set as the power budget per amplifier. The restriction on the summing circuit is not as critical, because there are 5 times fewer such circuits in the microscope. Contribution from the actual AC signals and various voltage regulators are negligible and are not taken into account.

Design Implementation

Evolution of the Design

The initial approach to this problem of gain switching was just that suggested by Photonique documentation: turning up the amplifier supply voltage. With the transistors' maximal voltage rating of 15 V taken as the high gain setting, some simulations were done to assess the amplifier performance. The following problems were found in this approach:

- Gain saturates with increasing supply voltage leading to poor gain separation between the two modes (recall that the low gain setting needs to be much lower for real signals.)

- Power consumption is of order 200 mW at high gain setting

- Component values necessary for high gain are not suitable for stable, -independent design

- Input impedance of the amplifier increase significantly in the high gain design. (This along with the SiPM capacitance sets the integration RC-time.) On the other hand, the effective impedance and therefore pulse shape varies with supply voltage.

A low-impedance input stage was designed to alleviate the last issue, but the rest remained serious concerns and challenges. An alternate design was adapted in which the supply voltage remains constant but the summing stage offers additional amplification. Gain selection is accomplished with a FET switch, effectively altering the resistance in a transistor stage similar to the common emitter amplifier.

Input Impedance

The low impedance input stage was retained from the earlier design and applied the the summing circuit, since it pools currents from the individual amplifiers. In Photonique's design, the input signal sees the transistor base, base-biasing resistor, and a feedback resistor in parallel. The new input stages take the signal on the emitter (base held at a set DC value), in which case the signal sees the emitter resistor and the impedance looking into the emitter in parallel with each other. The latter dominates with an effective resistance of order 25 Ω. The input stages are biased with generous amount of current to keep this value low.

-dependence and Voltage Buffering

There turned out to be a significant trade-off between gain achieved in the first amplification stage and β sensitivity. Since the variation in beta is cumulative in the progress of the signal through the amplifier, it is essential to keep the variation low at this point. For this reason, the gain has been turned down to around 400 Ω - well below the requirement set by the gain/dynamic range considerations themselves. This stage also draws significant current, accounting for about half the amplifier power budget, to keep this point minimally β-dependent.

To keep single channel and summing circuit readout independent of each other, a separate driver for the summing circuit was added. The first stage of the amplifier contains a switchable collector resistance which, the ratio of which with the effective resistance of the driver sets the additional gain sought at this stage. The additional inversion (to a positive-going signal) must be countered with another inverter, followed by the voltage buffer similar to that at the end of the single channel amplifier circuit.

Signal buffering turns out to be tricky in this project. The requirement of negative output pulse polarity set by the ADC mandates a PNP transistor for the final stages of both amplifier and summing segments. However, the β characteristics of the only acceptable fast PNP found on the market (BFT92W) are even worse than those in its NPN counterpart. The typical value of is 50 with a minimum value of 20, compared to BFR92P from Infineon, which sports values from 70 to near 100. The effective load of the terminators of about β50 Ω remains comparable to the source impedance of the circuit. In other words, the source impedance cannot be considered negligible compared to the load, creating an effective voltage divider whose ratio depends on beta! Since the output from the summing circuit suffers from about twice as much variation due to β because of all the preceding stages, a stiffer buffer became essential on this end. The emitter-follower driver was doubled, effectively multiply the β's of the two transistors. The resulting two diode drops, too low to avoid significant saturation on collectors of earlier stages, are countered with a DC level shift with AC coupling from preceding circuit elements.

A particularly challenging point in the circuit in terms of impedance turned out to be the junction with the common-emitter amplifier stage used as an inverter. At high gain, the effective source impedance is set to about 3.5 kΩ. Thus, this point suffers from significant loading down of the signal and subsequent sensitivity to β. Additionally, it was found that the low bandwidth characteristics of the common-emitter amplifier resulting from the Miller Effect - stray capacitance between transistor base and collector, magnified with about the gain of the amplifier. These concerns motivated insertion of another buffer between these stages, increasing the load seen by the preceding m transistor stage and decreasing the source impedance seen by the inverting amplifier stage (The characteristic time, RC, of the inherent integrator decreased proportionately.)

Dynamic Range

It essential to avoid clipping the signal at designed gain levels and to be able to utilize the full range (2 V) of the ADC. Appropriate DC level were set to avoid saturation any transistor collectors. This turns out a bit involved, since the collector-base voltage (plus the canonical saturation margin of 100 mV) gap necessary is more than the maximum desired signal of 2 V due to attenuation along the amplifier chain. Changing DC levels changes biasing of transistor bases, changing the quiescent current and therefore the attenuation. Additionally the power budget significantly restricts the DC levels of the circuit.

In the current stage of the design, full 2V range has not been achieved. Both single channel and summing outputs go up to about 1.5 V.

The Gain Switch

A MOSFET switches the effective collector resistance in the first stage of the summing circuit between about 3.3 kΩ due to Re alone and about 80 Ω for the parallel path. NXP's BF1108R has been selected for prototyping. Its typical for current pinch-off is -3 V (max: -4 V). Putting its source on the supply rail and switching the gate between 5 V (on) and 0 V (off). A bypass capacitor (not shown in diagram) near the gate lead is important to prevent spurious switching.

Final Performance Parameters

With the final parameters specified by the circuit model resistor input vector set to

R = [.56 1 .33 .47 1.36 1 .12 1.22 .1 .082 3.3 .15 .68 .18 2 .392 .7 1]*1e3

(see SiPM Amplifier Components for a complete list of component values) the following theoretical specifications are achieved:

| Amplifier Stage | Summing Stage | Units | Notes | |

|---|---|---|---|---|

| Gain (low/high) | 0.29 | 0.29/7.5 | kΩ | 50 Ω load assumed |

| Input impedance | 13.5 | 27.3 | Ω | |

| Power (quiescent) | 42 | 47 | mW | i.e. 52 mW/channel |

| Output pulse height (max) | 1.46 | 1.45 | V |