# F1TDC

# A High-Resolution, Multi-Hit, VME64x Time-to-Digital Converter

# User's Manual V1.1

23 April 2004

U.S. Department of Energy's

THOMAS JEFFERSON NATIONAL ACCELERATOR FACILITY

# **Table of Contents**

| 1 Introduction                                                                                          | 3                    |

|---------------------------------------------------------------------------------------------------------|----------------------|

| 2 Specifications                                                                                        | 4                    |

| 3 The F1TDC Architecture  3.1 The F1 ASIC Chip  3.2 Module Architecture  3.3 Configuring the F1TDC      | 5<br>5<br>7<br>8     |

| 4 Connections 4.1 Front Panel 4.1.1 Input Connectors 4.1.2 Timing & Control Connector 4.2 Backplane     | 10<br>10<br>11<br>13 |

| 5 Using the Module 5.1 Controlling the Module 5.2 Module Operation 5.3 Module Registers 5.4 Data Format | 15<br>16<br>17<br>22 |

| <u>Appendices</u>                                                                                       |                      |

| A – F1 ASIC Configuration Registers and Addresses                                                       | 25                   |

| B – Sample F1 ASIC Configuration Register Values                                                        | 34                   |

| C – F1 TDC Configuration Control Manual                                                                 | 35                   |

# 1 Introduction

# F1TDC - A VME64x High Resolution, Multi-Hit, Time-to-Digital Converter

- Multi-Hit, Differential ECL Inputs

- § High Resolution up to 60 pS LSB

- § Wide Dynamic Range up to 7.8 uS

- § High Stability by PLL Feedback Loop

- S Data Validation by Trigger Matching with Zero Suppression

- S Programmable Trigger Window and Latency

- S Data Storage up to 1 Million Hits

- § Flexible Control Inputs Via Front Panel or Backplane

- § VME64x Compliant with 2eVME Data Transfer Cycles

The F1TDC is a high resolution Time-to-Digital Converter (TDC). This module is particularly suited for applications requiring high-resolution time measurements with multi-hit capability at high event rates and where high channel densities are desirable. Wide dynamic range combined with trigger matching, zero suppression and deep storage alleviates the need for further data manipulation and reduces intermediate data storage requirements. A standard VME64x data acquisition bus guarantees the user will have high data throughput combined with long term industry support.

# **2** Specifications

**Packaging** 6U VME64x

*Inputs* Differential ECL (110 Ohm)

64 Channels @ 120 pS LSB 32 Channels @ 60 pS LSB

Control START, SYNCRES, TRIGGER

Front Panel – Differential ECL (110 Ohm) Backplane – Differential LVPECL (110 Ohm)

*Clock* Differential LVPECL (110 Ohm) – 40 MHz

Internal, Front Panel, Backplane

Dynamic 7.8 uS (for 120 pS LSB) Range 3.9 uS (for 60 pS LSB)

Standard Less than 0.9 LSB

**Deviation**

INL 0 LSB

**DNL** 10-50% LSB

Acquisition Trigger Matching w/ Zero suppression

Programmable Trigger Window and Latency

*FIFO* 1 M TDC Data Words

Interface 32-bit VME Block Transfers (>20 Mbyte/s)

64-bit VME Block Transfers (>40 Mbyte/s)

**Power** +12V @ 0.5A

-12V @ 0.4A +3.3V @ 7.3A +5V @ 1.8A

# 3 The F1TDC Architecture

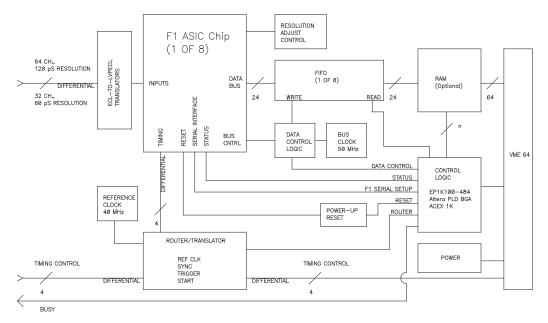

The block diagram for the F1TDC module is shown in figure 1.

The front-end section of the F1TDC encompasses the signal inputs with ECL-to-LVPECL translators, the timing control inputs, reference clock, router/translator, resolution adjust control and eight (8) F1 ASIC chips.

The back-end section encompasses the FIFOs, data bus control logic, initialization controls and VME64x interface functions.

Figure 1 – F1TDC Module Block Diagram

# 3.1 The F1 ASIC Chip

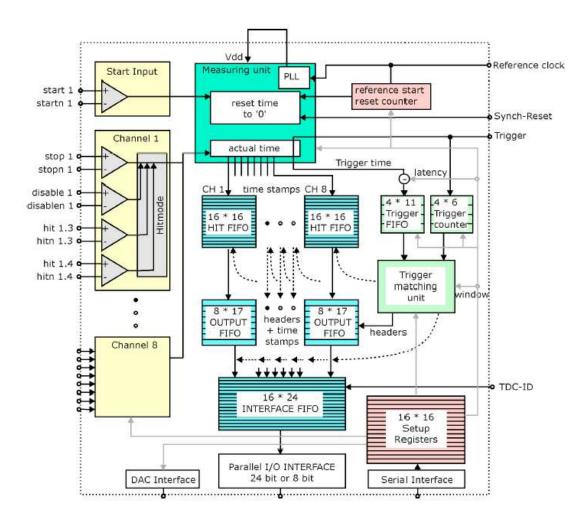

The core of our TDC module is the F1 TDC chip. A functional block diagram of the F1 ASIC chip is shown in figure 2. This chip uses purely digital delay techniques to measure time by means of a 19-tap asymmetric ring oscillator with phase-locked loop (PLL) control. Each of the pipelined F1 chips provides eight channels at 120 pS LSB or four channels at 60 pS LSB when a reference clock of 40 MHz is used. Internal FIFOs allow for storage of 16 hits per channel in leading and/or trailing edge modes. The following outline pertains to the use of the F1 chip in our TDC module.

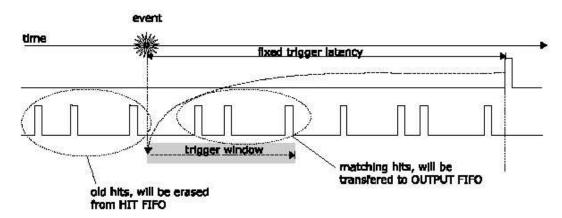

A key feature of the F1 chip is a Trigger Matching processing unit, which allows for selection of hits within a programmable time window and latency from the occurrence of a valid trigger input. Hits that fall outside of the window and latency settings are suppressed from the output buffer and cleared from the hit FIFO. Figure 3 depicts the operation of the trigger matching function.

Figure 2 - The F1 ASIC Chip

The trigger matching feature is used in common start/stop and synchronous measurement modes. In common start/stop mode, a *Start* signal resets the internal measurement counter and a *Trigger* signal sets the measurement window. Hits falling within these two signals will always be accepted by the trigger matching unit. In synchronous mode, a *Synch-Reset* signal is used to reset the internal measurement counter and thus synchronize all TDCs in an experiment. Internal start signals are automatically generated at a programmable rate. The trigger matching unit validates hits within the programmed window and latency. Headers and trailers identifying the channel, chip, trigger time and event number can be output to delineate events. The dynamic range is 7.8 uS at 120 pS LSB and 3.9 uS at 60 pS, with a 40 MHz *Reference Clock*.

To ensure stability and measurement reliability, each F1 chip is PLL-regulated against temperature drifts and manufacturing tolerances. The feedback loop employs a phase-frequency detector, a loop filter and a voltage regulator, which drives the substrate or core of the F1 chip. In this manner, delays within the internal Delay Locked Loop (DLL) are kept constant which translates into a stable LSB resolution or bin size.

The F1 chip is configured via a serial interface port, which accesses 16 registers. Readout of data is via a 24-bit parallel port.

Further information on the F1 ASIC Chip can be obtained by contacting **acammesselectronic gmbh** at www.acam.de .

Figure 3 - Trigger Matching

#### 3.2 Module Architecture

The eight F1 TDC chips on our module provide 64 channels in normal mode, or 32 channels in high resolution mode. Front panel input signal levels are differential ECL to be compatible with existing systems. Timing control signals are provided on the front panel and are also available through backplane connections for ease of system integration. A 128K word deep FIFO capable of simultaneous reads and writes is attached to each F1 TDC chip to buffer its output data. The VME interface and all control logic and registers are implemented in a single Field Programmable Gate Array (FPGA). All VME bus tranceivers are compatible with the high-speed protocols of the VME64x standard. The RAM shown in Figure 1 is an option not present on this version of the TDC.

Output data from the F1 TDC chip is ordered according to channel number (channel 0 first, channel 7 last). Within each channel, hit data is ordered from earliest to latest. Each F1 TDC chip may be configured to supply a header word for channel 0 and a trailer word for channel 7 in its output data stream whenever a trigger occurs. This takes place even if there is no valid hit data for the trigger. During readout, control logic uses these markers to switch between the FIFOs that supply the data. In this way, data from multiple chips that are associated with the same trigger may be assembled into an event fragment for the module. Individual channels may be disabled during configuration of the F1 TDC chips. The FIFO for an individual F1 TDC chip may also be bypassed from the readout sequence.

The module can be configured to set a flag in a register when the data from a programmed number of triggers is available in its buffers. This flag may be optionally used to interrupt the crate controller. Readout is accomplished most efficiently using a

block transfer protocol. Because the number of data words currently stored in the module is not available to the crate controller, a slave terminated block transfer is used instead. The crate controller is programmed to read out, via block mode, a number of words that is beyond the storage capacity of the module. During readout the module will provide the block of data associated with the programmed number of triggers. When this data is depleted the module terminates the block transfer by issuing a bus error (BERR). A register bit in the module is set when this occurs. The crate controller can query this bit to verify that the bus error was generated deliberately by the module and does not signify a system failure.

To enhance system performance a set of TDC modules may be read out as a single logical read using a multiblock protocol. This involves passing a token between modules along a private line. It is implemented in the following way. All TDC modules in the set are programmed to respond to a Common Address Range used exclusively for multiblock transfers. Only the TDC having the token will actually respond to such an address cycle. The TDC module of the set that is furthest left in the crate is configured to be the first module and initially claims the token. The module furthest to the right is set as the *last* module. All modules except the *last* one are configured to pass the token when they have transferred the programmed number of events. The last module is instead configured to respond with BERR. In addition, the *first* module may be configured to initiate readout by interrupting the crate controller when the data from a programmed number of triggers is available in its buffers. A slave terminated block transfer using the Common Address Range will accomplish the readout of the data from the programmed number of triggers for all boards of the set. When BERR occurs signaling the completion of this transfer, the first module seizes the token again.

## 3.3 Configuring the F1TDC

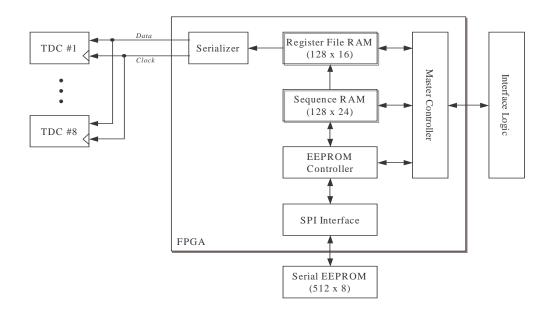

The TDC module contains eight F1 TDC devices that must be configured prior to operation. Each device contains sixteen 16-bit write-only configuration registers that are accessed through a synchronous serial bus. The TDC configuration control logic is implemented in the FPGA. It contains a serializer for the TDCs, a register file RAM, a configuration sequence RAM, an EEPROM controller, and host interface logic. An overview of the configuration control logic architecture is shown in Figure 4.

A 24-bit frame is transmitted to 8 TDCs on a synchronous serial bus. This frame consists of a 3-bit device address, one broadcast bit, a 4-bit register address, and 16-bit data. A TDC will accept a frame if its unique hardware address matches the device address transmitted in the frame.

The TDC configuration registers are write-only. Read-back is accomplished using a local copy of the registers stored in FPGA RAM. A 128x16 register file RAM stores all 16 registers from each of 8 TDCs. Any write to the register file will store the data in RAM and serialize the data to the TDCs. The serializer constructs the TDC data frame based on the register file address and write data.

Figure 4: F1 TDC Configuration Control Logic

For the TDCs to function properly, the TDC registers must be configured in a specific order. A configuration sequence RAM is provided to remove this burden from the host software. The 128x24 sequence RAM permits configuration of any register on any TDC in any order. This is accomplished by storing entire 24-bit serial data frames sequentially in RAM. A programmable end address is used to mark the end of sequence. When the configuration sequence is triggered, the RAM is read sequentially from address 0 to the end address. The 24-bit data is decoded and passed to the register file where it is stored and serialized.

A 512x8 serial EEPROM stores the sequence RAM and other user data. The EEPROM is accessed through an EEPROM controller and an SPI compatible interface. The controller provides a random access read/write interface to the EEPROM. It manages device opcodes, status, and data. The SPI interface contains a clock manager and a serializer/deserializer. Since the Sequence RAM and end address occupy only 385 bytes of the 512-byte EEPROM, the remaining space is available for user data.

The Master Controller module provides a host interface to the control logic and interconnects the register file, sequencer, and EEPROM modules. It permits read and write access to the Register File RAM, Sequence RAM, and EEPROM. The host can trigger TDC configuration from Sequence RAM and transfer of Sequence RAM to or from the EEPROM. At power-up, the Sequence RAM and end address are automatically loaded from EEPROM then passed to the register file and serializer to configure the TDCs. This automatic power-up configuration removes considerable software overhead for a large number of TDC boards. A description of all the configuration registers can be found in Appendix A. Sample values of the registers under various operating conditions are found in Appendix B.

#### 4.1 Connections – Front Panel

#### 4.1.1 Input Connectors

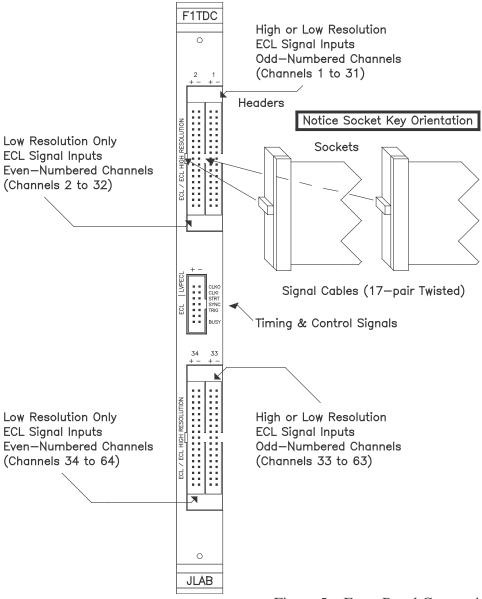

Time measurements are performed on differential ECL signals connected to the top and bottom stacked headers. Each header has 17 pairs of pins with the + (true) on the side of the orientation key (left side) and the – (complement) on the right side, as illustrated in figure 5, and differentially terminated into **110 Ohm** impedance. The 17<sup>th</sup> pair is not used or connected in any manner. Only the rightmost headers on each of the top and bottom stacks are used during high-resolution measurements. *Please, notice the orientation of the socket and cable when making connections to the module.*

Figure 5 – Front Panel Connections

#### 4.1.2 Timing & Control Connector

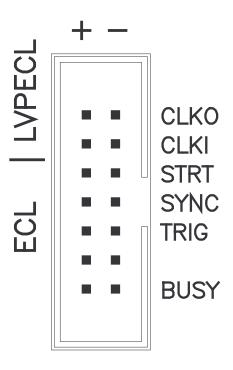

Timing and control signals are supplied through either the front panel or backplane. Front panel connections are appropriate for small data acquisition systems and require the user to provide connections to a 14-pin header by individual pair sockets or 14-pin socket with twisted-pair cable (figure 6). All inputs are differential and terminated into **110 Ohm** impedance.

Figure 6 – Timing & Control Signals

**CLK0** Reference Clock Output, Differential LVPECL, 40 MHz.

**CLKI** Reference Clock Input, Differential LVPECL, Capacitively Coupled.

STRT Start, Differential ECL Input - Resets the Internal Measurement Counter on all F1 ASIC Chips in Common Start/Stop Mode. The Signal Inputs Function as Stops.

SYNC Synch-Reset, Differential ECL Input – Resets the Internal Measurement Counter on all F1 ASIC Chips in Synchronous Mode.

TRIG Trigger, Differential ECL Input – Sets the Measurement Validation Window. The Trigger Window and Latency are Programmable During Configuration.

BUSY

Busy, Differential ECL Output – Data FIFO Memory Almost Full Condition. Triggers should be stopped to avoid loss of data.

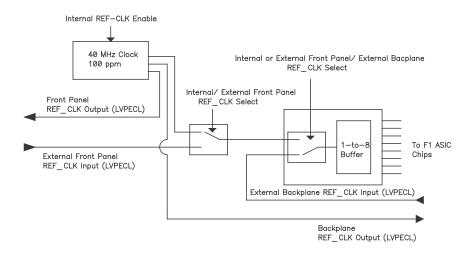

The user has the option of selecting the reference clock source through the VME interface. The internal reference clock source has a frequency stability of 100 ppm . As the timing resolution of the F1 ASIC Chips depends on the stability of the reference clock, the user should exercise caution when selecting and implementing external reference sources. Figure 7 shows a simplified diagram of the reference clock distribution. Note that all reference clock paths are differential and all the external LVPECL inputs are capacitively coupled for safety reasons. Systems employing PECL signals with receivers and sources powered from separate power supplies should have all inputs capacitively coupled as damage to receivers may occur when input signals forward bias the input ESD structures and the input base-collector junction of un-powered receivers.

Figure 7 – Reference Clock Distribution

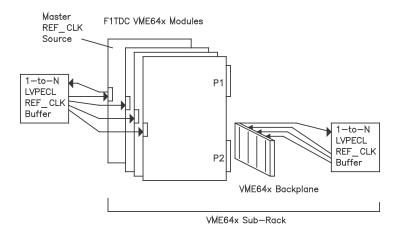

Once the internal REF-CLK is enabled, its output is always available at the front panel and the backplane. In systems with multiple modules and where clock synchronization is required, a single module can be configured as the REF\_CLK master clock. The use of an external LVPECL clock distribution module will then be required. Figure 8 illustrates possible implementations for small and large scale systems.

Figure 8 – REF\_CLK Distribution

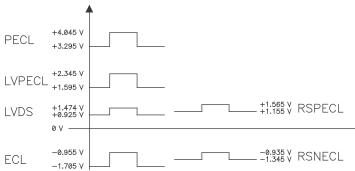

Larger systems employing multiple sub-racks may benefit from integration of the various timing and control signals into a single board located within each sub-rack, further providing ECL-to-LVPECL or Optical-to-LVPECL translation. Additional care should be taken to minimize signal skews. Figure 9 depicts various high-speed, differential signal standards.

Figure 9 – Typical High-Speed Differential Signal Standards

# 4.2 Connections – Backplane

The VME64x standard specifies that 160-pin DIN connectors be used for connectors P1 and P2. Tables 1 and 2 show the pin allocations for P1 and P2, respectively.

| Labl | e I | _ | РΙ | Pın | al. | locati | ion* |  |

|------|-----|---|----|-----|-----|--------|------|--|

|      |     |   | 7  |     |     |        | Λ    |  |

|    | Z      | A         | В        | С          | D      |

|----|--------|-----------|----------|------------|--------|

| 1  | MPR    | DV0       | BBSY*    | DV8        | VPC    |

| 2  | AGND   | DV1       | BCLR*    | DV9        | AGND   |

| 3  | MCLK   | DV2       | ACFAIL*  | DV10       | +V1    |

| 4  | AGND   | DV3       | BG0IO*   | DV11       | +V2    |

| 5  | MSD    | DV4       | BG0IO*   | DV12       | RsvU   |

| 6  | AGND   | DV5       | BG1IO*   | DV13       | -V1    |

| 7  | MMD    | DV6       | BG1IO*   | DV14       | -V2    |

| 8  | AGND   | DV7       | BG2IO*   | DV15       | RsvU   |

| 9  | MCTL   | AGND      | BG2IO*   | AGND       | GAP*   |

| 10 | AGND   | SYSCLK    | BG3IO*   | SYSFAIL*   | GA0*   |

| 11 | RESP*  | AGND      | BG3IO*   | BERRV*     | GA1*   |

| 12 | AGND   | DSV1*     | BR0*     | SYSRESETV* | +3.3IN |

| 13 | RsvBus | DSV0*     | BR1*     | LWV*       | GA2*   |

| 14 | AGND   | WV*       | BR2*     | AMV5       | +3.3IN |

| 15 | RsvBus | AGND      | BR3*     | AV23       | GA3*   |

| 16 | AGND   | DTACKV*   | AMV0     | AV22       | +3.3IN |

| 17 | RsvBus | AGND      | AMV1     | AV21       | GA4*   |

| 18 | AGND   | ASV*      | AMV2     | AV20       | +3.3IN |

| 19 | RsvBus | AGND      | AMV3     | AV19       | RsvBus |

| 20 | AGND   | IACKV*    | AGND     | AV18       | +3.3IN |

| 21 | RsvBus | IACKINV*  | SERA     | AV17       | RsvBus |

| 22 | AGND   | IACKOUTV* | SERB     | AV16       | +3.3IN |

| 23 | RsvBus | AMV4      | AGND     | AV15       | RsvBus |

| 24 | AGND   | AV7       | IRQV7*   | AV14       | +3.3IN |

| 25 | RsvBus | AV6       | IRQV6*   | AV13       | RsvBus |

| 26 | AGND   | AV5       | IRQV5*   | AV12       | +3.3IN |

| 27 | RsvBus | AV4       | IRQV4*   | AV11       | LI/I*  |

| 28 | AGND   | AV3       | IRQV3*   | AV10       | +3.3IN |

| 29 | RsvBus | AV2       | IRQV2*   | AV09       | LI/O*  |

| 30 | AGND   | AV1       | IRQV1*   | AV08       | +3.3IN |

| 31 | RsvBus | -12IN     | +5VSTDBY | +12IN      | AGND   |

| 32 | AGND   | +5IN      | +5IN     | +5IN       | VPC    |

Table 2 – P2 Pin allocation\*

|    | Z    | A             | В      | С             | D    |

|----|------|---------------|--------|---------------|------|

| 1  |      |               |        |               | _    |

| 1  | UD   | UD            | +5IN   | UD            | UD   |

| 2  | AGND | UD            | AGND   | LOOP          | UD   |

| 3  | UD   | UD            | RETRY* | LOOP          | UD   |

| 4  | AGND | UD            | AV24   | AGND          | UD   |

| 5  | UD   | UD            | AV25   | UD            | UD   |

| 6  | AGND | UD            | AV26   | +3.3IN        | UD   |

| 7  | UD   | UD            | AV27   | +3.3IN        | UD   |

| 8  | AGND | UD            | AV28   | +3.3IN        | UD   |

| 9  | UD   | UD            | AV29   | +3.3IN        | UD   |

| 10 | AGND | UD            | AV30   | AGND          | UD   |

| 11 | UD   | UD            | AV31   | +3.3IN        | UD   |

| 12 | AGND | UD            | AGND   | AGND          | UD   |

| 13 | UD   | UD            | +5IN   | UD            | UD   |

| 14 | AGND | UD            | DV16   | UD            | UD   |

| 15 | UD   | UD            | DV17   | UD            | UD   |

| 16 | AGND | UD            | DV18   | UD            | UD   |

| 17 | UD   | UD            | DV19   | AGND          | UD   |

| 18 | AGND | UD            | DV20   | SPARE_OUT_R   | AGND |

| 19 | UD   | UD            | DV21   | TOKEN_OUT_R   | AGND |

| 20 | AGND | UD            | DV22   | SPARE_IN_R    | AGND |

| 21 | UD   | UD            | DV23   | TOKEN_IN_R    | AGND |

| 22 | AGND | UD            | AGND   | BUSY_B_OUT-   | UD   |

| 23 | UD   | UD            | DV24   | BUSY_B_OUT+   | UD   |

| 24 | AGND | UD            | DV25   | AGND          | UD   |

| 25 | UD   | UD            | DV26   | TRIGGER_B_IN+ | UD   |

| 26 | AGND | UD            | DV27   | TRIGGER_B_IN- | UD   |

| 27 | UD   | UD            | DV28   | START_B_IN+   | UD   |

| 28 | AGND | UD            | DV29   | START_B_IN-   | UD   |

| 29 | UD   | UD            | DV30   | REFCLK_B_IN+  | UD   |

| 30 | AGND | AGND          | DV31   | REFCLK_B_IN-  | UD   |

| 31 | AGND | REFCLK_B_OUT- | AGND   | SYNCRES_B_IN- | AGND |

| 32 | AGND | REFCLK_B_OUT+ | +5IN   | SYNCRES_B_IN+ | VPC  |

<sup>\*</sup>Pins with shaded entries are not used.

# **5** Using the Module

## **5.1** Controlling the Module

Communication with the module is by standard VME bus protocols. All registers and memory locations are defined to be 4-byte entities. The VME slave module has three distinct address ranges.

<u>A24</u> – The base address of this range is set by a 12-element DIP switch on the board. It occupies 4 Kbytes of VME address space, organized in 1 K 32-bit words. Relative to the base address, this space is divided as follows:

000-7FF – Register space to control and monitor the module

800-FFF – F1 chip configuration space

Detailed information about the F1 chip configuration space is found in Appendix C. To summarize, the F1 chip configuration space is divided as follows:

800-9FF – Configuration register file. The 4-byte registers are ordered as:

Chip 0 register 0, 1, 2, ..., 15,

Chip 1 register 0, 1, 2, ..., 15,

Chip 7 register 0, 1, 2, ..., 15.

Direct writes to an F1 chip register may be made to the address:

Address = 800 + (40 \* chip #) + (4 \* register #).

The order in which the registers are written should be the following: register 15, 10, 0, 1, 2, 3, 4, 5, 6, 8, 9, 11, 12, 13, 14, 7.

Sample values of the F1 chip registers under several operating conditions are found in Appendix B.

A00-BFF – Setup RAM (see Appendix C).

C00-DFF – Configuration control registers (see Appendix C).

E00-FFF – Spare

<u>A32</u> - The base address of this range is programmed into register ADR32. It occupies 4 Mbytes of VME address space, organized in 1 M 32-bit words. <u>A read of any address in this range will yield the next TDC data word from the module.</u> Even though the module is

a FIFO, the expanded address range allows the VME master to increment the address during block transfers. This address range can participate in single cycle, 32-bit block, and 64-bit block reads. The only valid write to this address range is the data value 0x80000000 which re-enables the module to generate interrupts (after one has occurred). The address range must be enabled by setting ADR32[0] = 1.

<u>A32</u> - The lower and upper limits of this address range are programmed into register ADR\_MB. This common address range for a set of TDC modules in the crate is used to implement the Multiblock protocol. By means of token passing TDC data may be read out from multiple TDC modules using a single logical block read. <u>The board possessing the token will respond to a read cycle in this address range with the next TDC data word from that module.</u> The token is passed along a private daisy chain line to the next module when it has transferred all data from a programmed number of events (register EVENT LEVEL). The address range must be enabled by setting ADR\_MB[0] = 1.

## **5.2** Module Operation

The following describes the setup and operation of the TDC in single and multiple module applications.

<u>Single Module</u> – After a reset of the module (CSR[31] = 1), the F1 chip configuration registers may be written directly through the A24 address space (800-9FF). The source for the control signals is set to Front (CTRL[0] = 0) and the internal clock is selected and turned on (CTRL[2] = 0, CTRL[1] = 1). The EVENT LEVEL register is loaded with the number of events (i.e. triggers) that constitute a *block*. The INTERRUPT register may be loaded with the interrupt ID and level if the module is to initiate an interrupt when the defined *block* of data is available for readout. The address for data access is loaded (ADR32), and the F1 chips that are to participate in the readout are selected (CTRL[23...16]). The event level interrupt (CTRL[3] = 1) is enabled if interrupt generation is desired. The BERR response is enabled (CTRL[6] = 1) to allow the module to indicate when the complete *block* of data has been read out.

When the programmed number of triggers has been received, the *event level flag* (CSR[3]) will be set and an interrupt will be generated if enabled. The user should initiate a DMA block read (32 or 64-bit) from the address in stored in ADR32. The length of the block read should be programmed to be larger than the expected size of the data *block* (e.g. 4 Mbytes). The module will terminate the DMA transfer by issuing BERR when all data from the *block* has been transferred. Interrupt generation must be re-enabled by writing 0x80000000 to the address in ADR32.

<u>Multiple Modules</u> – All modules should be reset and loaded with the configuration register values as described above for a single module. The source of the control signals for the modules is set to Front or Back depending on the distribution system used. The internal clocks need not be turned on, as a clock source is provided as part of the distribution system. The EVENT LEVEL register and the chips selected for readout are loaded into each module. A unique address for data access is loaded into ADR32 for each

module. The <u>common</u> address range for the Multiblock protocol is loaded into ADR\_MB for each module. All modules are programmed to participate in the Multiblock protocol (CTRL[7] = 1). The *left-most* TDC module in the system is programmed as the *first* module (CTRL[8] = 1), and the *right-most* TDC module is designated the *last* module (CTRL[9] = 1). For the *first* module, the INTERRUPT register may be loaded and the event level interrupt bit enabled, if desired. The BERR response is enabled for the *last* module only. For backplane mounted signal distribution systems, the *token* passing lines are included in the system. Front signal distribution systems need additional connections to the backplane for token passing lines (see Table 2).

When the programmed number of triggers has been received, the *event level flag* will be set in each module and an interrupt will be generated by the *first* module (if enabled). The user should initiate a DMA block read (32 or 64-bit) from the address stored in ADR\_MB. The length of the block read should be programmed to be larger than the total size of data from all modules (e.g. 4 Mbytes x # modules). Since the *first* module initially has the *token*, it will respond with data to the VME bus cycles. When data from the *first* module's block has been depleted, it passes the *token* to the next module in the chain. This module will respond with data until its data block is exhausted and the *token* is passed to the next module. The *last* module will terminate the DMA transfer by issuing BERR when all data from its *block* has been transferred. Upon detecting BERR, the *first* module takes possession of the *token*. Interrupt generation must be re-enabled by writing 0x80000000 to the address in ADR32 of the *first* module.

#### **5.3 Module Registers**

#### <u>CSR – Control/Status</u> (0x0)

```

0 - (R/W) – spare control bit

```

1 - (R/W) - TDC chip configuration error (writing 1 clears status)

2 - (R) - TDC chip configuration active

3 - (R) – event level flag asserted

4 - (R) – zero events in buffer

5 - (R) - BERR status

6 - (R) – Token status

7 - (R) - ERROR condition exists for an enabled TDC chip

8 - (R) - TDC chip 0 error

9 - (R) - TDC chip 1 error

```

10 - (R) - TDC chip 2 error

```

$$11 - (R) - TDC$$

chip 3 error

$$12 - (R) - TDC$$

chip 4 error

$$13 - (R) - TDC$$

chip 5 error

$$14 - (R) - TDC$$

chip 6 error

$$15 - (R) - TDC$$

chip 7 error

$$16 - 23$$

(R) – Output Enable for external FIFO  $0 - 7$

$$24 - 27 -$$

(not used)

$$28 - (W) - Pulse Spare Out (if CTRL[12] = 1)$$

$$29 - (W) - Pulse Soft Trigger (if CTRL[5] = 1)$$

#### CTRL - Control (0x4)

$$0 - (R/W) - Front/Back Control Signals select (0 = Front, 1 = Back)$$

$$1 - (R/W) - Internal Clock Control (0 = Clock OFF, 1 = Clock ON)$$

$$2 - (R/W) - Clock Select (0 = Internal (if CTRL[0] = 0), 1 = External)$$

- 3 (R/W) Enable Event Level Interrupt

- 4 (R/W) Enable Error Interrupt

- 5 (R/W) Enable Soft Trigger

- 6 (R/W) Enable BERR response

- 7 (R/W) Enable Multiblock protocol

- 8 (R/W) FIRST board in Multiblock system

9 – (R/W) – LAST board in Multiblock system

10 – (R/W) – Enable readout of all F1 chip headers/trailers

11 - (R/W) – Enable BUSY output to front panel

12 – (R/W) – Enable Spare output

13 - 15 - (not used - read as 0)

16 - 23 (R/W) – Enable Readout from TDC 0 - 7

24 - 31 -(not used – read as 1)

#### EVENT COUNT (0x8)

[15...0] - (R) – Event Count[15...0]. Event Count =  $0 \rightarrow CSR[4] = 1$ .

[31...16] – (not used)

#### EVENT LEVEL (0xC)

[15...0] - (R/W) - Event Level[15...0]. Event Count  $\geq$  Event Level  $\rightarrow$  CSR[3] = 1.

[31...16] – (not used)

#### INTERRUPT (0x10)

[7...0] - (R/W) - Interrupt ID (vector)

[10...8] - (R/W) - Interrupt Level [2..0]. Valid values = 1,...,7.

11 - 15 - (not used)

[20...16] – (R) – Geographic Address (slot number) in VME64x chassis.

21 - 22 - (not used)

23 – (R) – Parity Error in Geographic Address.

24 - 31 - (not used)

#### <u>ADR32 – Address for data access</u> (0x14)

0 - (R/W) – Enable 32-bit address decoding

1 - 5 – (not used – read as 0)

[15...6] – (R/W) – Base Address for 32-bit addressing mode (4 Mbyte total)

#### <u>ADR\_MB – Multiblock Address for data access</u> (0x18)

0 – (R/W) – Enable Multiblock address decoding

1 - 5 – (not used – read as 0)

[15...6] – (R/W) – Lower Limit address (ADR\_MIN) for Multiblock access

16 - 21 -(not used – read as 0)

[31...22] – (R/W) – Upper Limit address (ADR\_MAX) for Multiblock access

The board that has the TOKEN will respond with data when the VME address satisfies the following condition:

$$ADR_MIN \leq Address < ADR_MAX.$$

#### TDC STATUS (4 registers)

(bits 0 - 15 for chip 'A', bits 16 - 31 for chip 'B')

- 0 Resolution LOCKED (A)

- 1 TDC Hit FIFO Overflow (A)

- 2 TDC Trigger FIFO Overflow (A)

- 3 TDC Output FIFO Overflow (A)

- 4 External FIFO Full (A)

- 5 External FIFO Almost Full BUSY asserted if chip enabled (A)

- 6 External FIFO Empty (A)

- 7 TDC Initialized (A)

- 8 Loss of Resolution Lock Occurred (A)

- 9 TDC Hit FIFO Overflow Occurred (A)

- 10 TDC Trigger FIFO Overflow Occurred (A)

- 11 TDC Output FIFO Overflow Occurred (A)

- 12 External FIFO Full Occurred (A)

- 13 15 (not used read as 0)

- 16 Resolution LOCKED (B)

- 17 TDC Hit FIFO Overflow (B)

- 18 TDC Trigger FIFO Overflow (B)

- 19 TDC Output FIFO Overflow (B)

- 20 External FIFO Full (B)

- 21 External FIFO Almost Full BUSY asserted if chip enabled (B)

- 22 External FIFO Empty (B)

- 23 TDC Initialized (B)

- 24 Loss of Resolution Lock Occurred (B)

- 25 TDC Hit FIFO Overflow Occurred (B)

- 26 TDC Trigger FIFO Overflow Occurred (B)

- 27 TDC Output FIFO Overflow Occurred (B)

- 28 External FIFO Full Occurred (B)

- 29 31 -(not used read as 0)

#### 5.4 Data Format

The F1TDC chip outputs 24-bit words. The words are of 2 types: header/trailer and data. The header/trailer words are used as event or channel separators, and provide information such as the event number and trigger time. A data word contains the time measurement for a hit. The bit assignments are shown below.

| Header / Trailer word | 0 |                          | 1 Bit   | 6 Bit           | 9 Bit           | 1 Bit                 | 3 Bit           | 3 Bit              |

|-----------------------|---|--------------------------|---------|-----------------|-----------------|-----------------------|-----------------|--------------------|

|                       |   | Trigger FIFO<br>overflow |         | Event<br>number | Trigger<br>time | Xor setup<br>register | Chip<br>address | Channel<br>address |

| data word             | 1 | 0                        | 3 Bit   | 3 Bit           | 36<br>0         | 1                     | 6 Bit           |                    |

| time measurement      |   |                          | Chip    | Chann           | el              | Time                  |                 |                    |

|                       |   |                          | address | addres          | s               |                       |                 |                    |

The header/trailer words can be enabled for each channel of the chip. In this case the output stream of data words for a trigger appears as follows:

```

header – channel 0

data – channel 0, earliest hit

...

data – channel 0, latest hit

trailer – channel 0

header – channel 1

data – channel 1, earliest hit

...

data – channel 1, latest hit

trailer – channel 1

...

header – channel 7

data – channel 7, earliest hit

...

data – channel 7, latest hit

trailer – channel 7, latest hit

```

In this case, the headers/trailers take up space in the F1TDC chip's output buffer while providing redundant information. A better solution is to enable only the header for channel 0, and the trailer for channel 7. The chip data stream then appears as follows:

```

header – channel 0

data – channel 0, earliest hit

...

data – channel 0, latest hit

data – channel 1, earliest hit

...

data – channel 1, latest hit

...

data – channel 7, earliest hit

...

data – channel 7, latest hit

trailer – channel 7

```

In our application of the F1TDC chip, we require that at least the header for channel 0 and the trailer for channel 7 be enabled for each chip that is to be read out. (The chips to be read out are specified by CTRL[23...16]). This minimal header/trailer information is used to assemble event fragments from different chips into a single event fragment that is associated with a given trigger for the board.

During readout, the default mode is to suppress all headers/trailers *except* the *header* for channel 0 of the *first* chip enabled for readout and the *trailer* for the *last* chip enabled for readout. If all chips 0-7 are enabled, the data from the board associated with a trigger will appear as follows:

```

header – chip 0, channel 0

data – chip 0, channel 0, earliest hit

...

data – chip 0, channel 0, latest hit

...

data – chip 0, channel 7, earliest hit

...

data – chip 0, channel 7, latest hit

...

data – chip 7, channel 0, earliest hit

...

data – chip 7, channel 0, latest hit

...

data – chip 7, channel 0, latest hit

...

```

data – chip 7, channel 7, earliest hit

...

data – chip 7, channel 7, latest hit

trailer – chip 7, channel 7

Whenever a suppressed intermediate chip header/trailer indicates an *error condition* (Trigger FIFO overflow) it will be *forced* into the data stream so that this condition will not be missed All intermediate chip headers/trailers can be forced to be read out by setting register bit CTRL[10] = 1.

The data word transferred across the VME bus includes the 24-bit TDC word and additional board location and F1TDC chip error information, as follows:

<u>DATA - module data word</u> (4 Mbyte address range, base programmed in register ADR32)

[23...0] – F1 chip word

24 – F1 chip Hit FIFO Overflow

25 – F1 chip Output FIFO Overflow

26 – F1 chip Resolution Locked

[31...27] – Slot ID

Slot ID = 1-21 indicates valid data. The module will return Slot ID = 30 when the data is not valid (e.g. an empty module is read, or data is not yet ready to be extracted). Slot ID = 0 is the tag for a 'filler' word. This is a non-valid data word that is inserted to make the block of data output from the module consist of an *even* number of words. (An even number of words simplifies 64-bit readout mode.) Data should be ignored if Slot ID = 0 or 30.

# Appendix A – F1 ASIC Configuration Registers and Addresses

The F1 ASIC Chip contains sixteen (16), 16-bit registers which can be programmed for specific applications and requirements and must be downloaded in a specific order. The following tables provide detailed information on register functionality. However, note that some registers may not be available to the user of the F1TDC module.

| Addr | D15   | D14               | D13   | D12     | D11    | D10    | D9       | D8   | D7     | D6     | D5     | D4   | D3    | D5      | D1  | DO  |

|------|-------|-------------------|-------|---------|--------|--------|----------|------|--------|--------|--------|------|-------|---------|-----|-----|

| 0    | 1     |                   |       | hea     | den    |        |          |      |        |        |        | tr   | ailen |         |     |     |

| 1    | hires | hitm              | letra | S       | q      | fake   | ovlap    | - 1  | bs     | obsp   | m_in   |      | slov  | N       |     | DA  |

| 5    | fe2   | re2               |       | 111 127 | adj    | ch2    |          |      | fe1    | re1    | adjch1 |      |       | 5000    |     |     |

| 3    | fe4   | re4               |       |         | adj    | ch4    |          |      | fe3    | re3    |        |      | adj   | ch3     |     |     |

| 4    | fe6   | re6               |       |         | adj    | ch6    |          |      | fe5    | re5    |        |      | adj   | ch5     |     |     |

| 5    | fe8   | re8               |       |         | adjch8 |        |          | fe7  | re7    | adjch7 |        |      |       |         |     |     |

| 6    | 1     | buscikdel adjch10 |       |         |        |        | h10      |      |        |        |        | adj  | ch9   |         |     |     |

| 7    | beini |                   |       |         |        | refont |          |      |        |        |        |      | h     | itt     |     |     |

| 8    | 1     |                   |       |         |        |        |          | tr   | rigwin |        |        |      |       |         |     |     |

| 9    | T     |                   |       |         |        |        |          | t    | riglat |        |        |      |       |         |     |     |

| 10   | don1  | pll               | track | neg     | r_adj  |        | efclkdiv |      | 1      |        |        | h    | sdiv  |         |     |     |

| 11   | 1     |                   |       | da      | c 2    |        |          |      |        |        |        | d    | sc 1  |         |     |     |

| 12   | I     |                   |       | da      | c 4    |        |          |      | T      |        |        | d    | ac 3  |         |     |     |

| 13   | dac 6 |                   |       |         |        |        |          |      |        |        | d      | ac 5 |       |         |     |     |

| 14   |       | 20                |       | da      | c 8    |        | . 0.     |      |        |        |        | d    | ac 7  | gu - 00 |     |     |

| 15   | don2  | htest             | stest |         |        |        | 120      | - 27 | dia3   | dia2   | dia1   | diaO | rosta | sync    | com | 8/2 |

| Paragraph   Para   | Adr  | Name                                     | Description                     | Adr   | Name          | Description                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------------------------|---------------------------------|-------|---------------|-----------------------------|

| hite set high resolution mode hitm set hit mode set Leading/trailing mode set Leading/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/trailing/traili | 0    | headen                                   | Enable header output            | 7     | beini         | initialize chip.            |

| hitm set hit mode set Leading/trailing mode set Leading/trailing mode safety bits, set to '0' 9 triglat trigger latency overlap hit mode ibs safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits, set to '0' pli test PLL obspd safety bits,  |      | trailen                                  | Enable trailer output           |       |               |                             |

| lerte sq safety bits, set to '0' 9 triglat trigger latency fake periodicity of fake triggers ovlap overlap hit mode ibs safety bits, set to '0' pll test PLL obspd safety bits, set to '0' track cut regulation loop of PLL m_in disable all signal inputs neg invert phase output of PLL slow safety bits, set to '0' refclkdiv reference clock divider PLL by this set to '0' refclkdiv reference clock divider PLL cell activate falling edges chan.2.1 re2.1 activate rising edges chan.2.1 leading.2.1 delay adjustments chan. 2.1 leading.3 activate rising edges chan.4.3 activate rising edges chan.4.3 adjoh4.3 activate rising edges chan.4.3 leading.4 dac 8.7 DAC data  fe6.5 activate falling edges chan.6.5 adjoh6.5 delay adjustments chan. 6.5 leading.5 adjoh6.5 delay adjustments chan. 8.7 leading.5 purposes, set '0' for diagnosis purposes, set '0' for diagnosis purposes, set '0' for diagnosis purposes, set '0' adjoh8.7 delay adjustments chan. 8.7 dia2 for diagnosis purposes, set '0' for diagno | 1    | hires                                    | set high resolution mode        |       |               |                             |

| sq safety bits, set to 'D' get triggers ovlap overlap hit mode overlap hit mode obspice safety bits, set to 'D' bits, set to  |      | hitm                                     | set hit mode                    | 8     | trigwin       | trigger window width        |

| fake ovlap overlap hit mode overlap hit  |      | lerta                                    | set Leading/trailing mode       |       | (170)         |                             |

| ovlap ibs safety bits, set to 'O' pill test PLL obspd safety bits, set to 'O' track cut regulation loop of PLL in men in disable all signal inputs slow safety bits, set to 'O' refckdiv need invert phase output of PLL switch on resolution adjust reference clock divider PLL hediv high speed divider PLL hedivider PLL hediv high speed divider PLL hediv high speed di |      | sq                                       | safety bits, set to 'O'         | 9     | triglat       | trigger latency             |

| ibs obspd safety bits, set to 'O' track cut regulation loop of PLL min disable all signal inputs safety bits, set to 'O' redignosis purposes, set 'O' read; cut regulation loop of PLL min disable all signal inputs safety bits, set to 'O' reficked reference clock divider PLL switch on resolution adjust refecked reference clock divider PLL hadiv high speed divider  |      | fake                                     | periodicity of fake triggers    |       | 338-358-355   |                             |

| obspd safety bits, set to 'O' track cut regulation loop of PLL m_in disable all signal inputs safety bits, set to 'O' pafety bits, set to 'O' pagety bits, set to 'O' pagety bits, set 'O' pagety bits, set 'O' pagety bits, set to 'O' pagety bits, set to 'O' pagety bits, set 'O' pagety bits, set 'O' pagety bits, set to 'O' pagety bits, s |      | ovlap                                    | overlap hit mode                | 10    | don1          | diagnosis mode              |

| m_in slow safety bits, set to 'O' r_adj switch on resolution adjust.  DA Start data transfer to DAC refolkdiv reference clock divider PLL high speed divider high speed divider high speed divider high speed divider high speed divi |      | ibs                                      | safety bits, set to 'O'         |       | pii           | test PLL                    |

| slow DA Start data transfer to DAC refelkdiv reference clock divider PLL high speed divider |      | obspd                                    | safety bits, set to 'O'         |       | track         | cut regulation loop of PLL  |

| slow DA Start data transfer to DAC refelkdiv reference clock divider PLL high speed divider |      | m in                                     | disable all signal inputs       |       | nea           | invert phase output of PLL  |

| DA Start data transfer to DAC refckdiv hadiv reference clock divider PLL high speed divider |      |                                          |                                 |       |               |                             |

| fe2,1 activate falling edges chan.2,1 re2,1 activate rising edges chan.2,1 adjch2,1 delay adjustments chan. 2,1 12 dac 4,3 DAC data  fe4,3 activate rising edges chan.4,3 re4,3 activate rising edges chan.4,3 adjch4,3 delay adjustments chan. 4,3 13 dac 6,5 DAC data  fe6,5 activate falling edges chan.6,5 re6,5 activate rising edges chan.6,5 delay adjustments chan. 6,5 test for diagnosis purposes, set 'O' stest for diagnosis purposes, set 'O' activate rising edges chan.8,7 re8,7 activate rising edges chan.8,7 dia3 for diagnosis purposes, set 'O' activate rising edges chan.8,7 dia2 for diagnosis purposes, set 'O' adjch8,7 delay adjustments chan. 8,7 dia1 for diagnosis purposes, set 'O' dia0 for diagnosis purpo |      | DA                                       | Start data transfer to DAC      |       | refclkdiv     | reference clock divider PLL |

| fe2,1 activate falling edges chan.2,1 re2,1 activate rising edges chan.2,1 adjch2,1 delay adjustments chan. 2,1 12 dac 4,3 DAC data  fe4,3 activate rising edges chan.4,3 re4,3 activate rising edges chan.4,3 adjch4,3 delay adjustments chan. 4,3 13 dac 6,5 DAC data  fe6,5 activate falling edges chan.6,5 re6,5 activate rising edges chan.6,5 delay adjustments chan. 6,5 test for diagnosis purposes, set 'O' stest for diagnosis purposes, set 'O' activate rising edges chan.8,7 re8,7 activate rising edges chan.8,7 dia3 for diagnosis purposes, set 'O' activate rising edges chan.8,7 dia2 for diagnosis purposes, set 'O' adjch8,7 delay adjustments chan. 8,7 dia1 for diagnosis purposes, set 'O' dia0 for diagnosis purpo |      |                                          |                                 |       | hsdiv         | high speed divider PLL      |

| re2.1 adjch2.1 activate rising edges chan.2.1 11 dac 2.1 DAC data  3 fe4,3 activate falling edges chan.4.3 adjch4.3 activate rising edges chan.4.3 13 dac 6.5 DAC data  4 fe8,5 activate falling edges chan.6.5 re6,5 activate rising edges chan.6.5 delay adjustments chan. 6.5 best for diagnosis mode delay adjustments chan. 6.5 fe8.7 activate falling edges chan.8.7 dia3 for diagnosis purposes, set 'O' stest for diagnosis purposes, set 'O' activate rising edges chan.8.7 dia2 for diagnosis purposes, set 'O' adjch8.7 delay adjustments chan. 8.7 dia1 for diagnosis purposes, set 'O' diagnosis  | 2    | fe2.1                                    | activate falling edges chan.2.1 |       |               |                             |

| adjch2.1 delay adjustments chan. 2.1  12 dac 4.3 DAC data  fe4.3 activate falling edges chan.4.3 adjch4.3 delay adjustments chan. 4.3  4 fe8.5 activate rising edges chan.6.5 re6.5 activate rising edges chan.6.5 delay adjustments chan. 6.5  5 fe8.7 activate falling edges chan.8.7 re8.7 activate rising edges chan.8.7 dia3 for diagnosis purposes, set 'O' stest for diagnosis purposes, set 'O' di |      | re2.1                                    |                                 | 11    | dac 2.1       | DAC data                    |

| 12 dac 4.3 DAC data  fe4,3 activate rising edges chan.4.3 adjch4.3 delay adjustments chan. 4.3  4 fe6,5 activate rising edges chan.6.5 re6,5 adjch6,5 delay adjustments chan. 6.5  5 fe8,7 activate falling edges chan.8,7 re8,7 activate rising edges chan.8,7 delay adjustments chan. 8,7  6 buscikdel delay for skewed bus clock adjch10,11 delay adjustments ref. chan.  12 dac 4,3 DAC data  13 dac 6,5 DAC data  14 dac 8,7 DAC data  15 don diagnosis mode for diagnosis purposes, set 'O' stest for diagnosis purposes, set 'O' diagnosis purp |      | adich2.1                                 |                                 |       |               |                             |

| 3 fe4,3 activate falling edges chan.4,3 activate rising edges chan.4,3 adjoh4,3 delay adjustments chan. 4,3  4 fe6,5 activate rising edges chan.6,5 re6,5 activate rising edges chan.6,5 delay adjustments chan. 6,5  5 fe8,7 activate falling edges chan.8,7 re8,7 activate rising edges chan.8,7 dia3 for diagnosis purposes, set 'O' activate rising edges chan.8,7 dia3 for diagnosis purposes, set 'O' activate rising edges chan.8,7 dia1 for diagnosis purposes, set 'O' adjoh8,7 delay adjustments chan. 8,7 dia1 for diagnosis purposes, set 'O' dia0 for diagnosis purposes, set 'O' set start ring oszillator synchronous mode common mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      | (1) - 10 - 10 - 10 - 10 - 10 - 10 - 10 - |                                 | 12    | dac 4.3       | DAC data                    |

| re4.3 activate rising edges chan.4,3 adjoh4.3 activate falling edges chan.6,5 re6,5 activate rising edges chan.6,5 adjoh6,5 adjoh6,5 adjoh6,5 adjoh6,5 adjoh6,5 adjoh6,5 activate falling edges chan.8,7 activate rising edges chan.8,7 re8,7 activate rising edges chan.8,7 adjoh8,7 adjoh8,7 delay adjustments chan. 8,7 dia2 for diagnosis purposes, set 'O' adjoh8,7 delay adjustments chan. 8,7 dia1 for diagnosis purposes, set 'O' adjoh8,7 delay adjustments chan. 8,7 dia2 for diagnosis purposes, set 'O' adjoh8,7 delay adjustments chan. 8,7 dia2 for diagnosis purposes, set 'O' adjoh8,7 delay adjustments chan. 8,7 dia2 for diagnosis purposes, set 'O' adjoh8,7 delay adjustments ref. chan.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3    | fe4.3                                    | activate falling edges chan 4.3 |       |               |                             |

| adjch4,3  delay adjustments chan. 4,3  4  fe8,5 re6,5 adjch6,5 delay adjustments chan. 6,5  fe8,7 re8,7 adjch8,7 delay adjustments chan. 8,7 d |      |                                          |                                 | 13    | dac 6.5       | DAC data                    |

| 4 fe6,5 activate falling edges chan.6,5 re6,5 adjch6,5 delay adjustments chan. 6,5 te8,7 activate rising edges chan.8,7 re8,7 activate rising edges chan.8,7 delay adjustments chan. 8,7 dia2 for diagnosis purposes, set 'O' adjch8,7 delay adjustments chan. 8,7 dia2 for diagnosis purposes, set 'O' diagnosis purp |      |                                          |                                 |       |               |                             |

| 4 fe8,5 activate falling edges chan.6,5 re6,5 activate rising edges chan.6,5 delay adjustments chan. 6,5 15 don diagnosis mode for diagnosis purposes, set 'O' stest for diagnosis purposes, set 'O' for diagnosis purposes, set 'O' diagnosis purposes, set ' |      | COMPANIES CONTRACT                       |                                 | 14    | dac 8.7       | DAC data                    |

| re6,5 adjch6,5 delay adjustments chan. 6,5 don diagnosis mode for diagnosis purposes, set 'O' stest for diagnosis purposes, set 'O' stest for diagnosis purposes, set 'O' for diagnosis purposes, set 'O' diagnosis purposes, set  | 4    | fe6.5                                    | activate falling edges chan 6.5 | 1515  |               |                             |

| adjch6,5  delay adjustments chan. 6,5  htest for diagnosis purposes, set 'O' stest for diagnosis purposes, set 'O' stest for diagnosis purposes, set 'O' diagnosis purpose |      |                                          |                                 | 15    | don           | diagnosis mode              |

| 5 feB,7 activate falling edges chan.B,7 dia3 for diagnosis purposes, set 'O' reB,7 activate rising edges chan.B,7 dia2 for diagnosis purposes, set 'O' diagnosis purposes, |      |                                          |                                 | 22.07 |               |                             |

| 5 feB,7 activate falling edges chan.8,7 dia3 for diagnosis purposes, set '0' re8,7 activate rising edges chan.8,7 dia2 for diagnosis purposes, set '0' adjch8,7 delay adjustments chan. 8,7 dia1 for diagnosis purposes, set '0' dia0 for diagnosis purposes, set '0' dia0 for diagnosis purposes, set '0' dia0 successive for diagnosis purposes, set '0' dia0 for diagnosis purposes, set ' |      | 8. 8.                                    |                                 |       | stest         |                             |

| re8.7 activate rising edges chan 8.7 dia2 for diagnosis purposes, set '0' adjch8.7 delay adjustments chan. 8.7 dia1 for diagnosis purposes, set '0' dia0 for diagnosis purposes, set '0' dia0 for diagnosis purposes, set '0' buscikdel delay for skewed bus clock rosta start ring oszillator sync delay adjustments ref. chan. sync synchronous mode common mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5    | fe8.7                                    | activate falling edges chan 8.7 |       | 50.00 TO 70.0 |                             |

| adjch8,7 delay adjustments chan. 8,7 dia1 for diagnosis purposes, set '0' dia0 for diagnosis purposes, set '0' dia0 for diagnosis purposes, set '0' start ring oszillator osza delay adjustments ref. chan. sync synchronous mode common mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -    |                                          |                                 |       |               |                             |

| 6 buscikdel delay for skewed bus clock rosta start ring oszillator adjoh10,11 delay adjustments ref. chan. sync synchronous mode common mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |                                          |                                 |       |               |                             |

| 6 buscikdel delay for skewed bus clock rosta start ring oszillator adjch1D,11 delay adjustments ref. chan. sync synchronous mode common mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      | 0010,                                    | acia, aajassiianis siiani a,    |       | (20.20)       |                             |

| adjch1D,11 delay adjustments ref. chan. sync synchronous mode com common mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6    | buscikdel                                | delay for skewed bus clock      |       |               |                             |

| com common mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.00 |                                          |                                 |       | 90000000000   |                             |

| 7.747                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      | aajai, 10, 11                            | acidy adjacontants for chair.   |       |               |                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |                                          |                                 |       | 8/24          | 8bit/24bit data output      |